1: ののの ★ 2017/05/19(金) 17:52:20.08 ID:CAP_USER.net

周藤瞳美 [2017/05/19]

産業技術総合研究所(産総研)などは5月16日、次世代の不揮発性メモリであるとされる磁気ランダムアクセスメモリ(MRAM)の3次元積層プロセス技術を開発したと発表した。

同成果は、産総研スピントロニクス研究センター金属スピントロニクスチーム 薬師寺 啓研究チーム長、集積マイクロシステム研究センター高木秀樹総括研究主幹、ウエハレベル実装研究チーム 倉島優一主任研究員、ナノエレクトロニクス研究部門3D集積システムグループ 菊地克弥研究グループ長、渡辺直也主任研究員らの研究グループによるもので、5月15日付けの国際科学誌「Applied Physics Express」に掲載された。

MRAMは、垂直磁化TMR素子をベースとする記録ビットと、ビット選択に用いる半導体トランジスタ(CMOS)、多結晶銅などの金属配線からなり、通常、垂直磁化TMR素子薄膜(TMR薄膜)は、逐次積層といってCMOS形成後に金属配線上に直接形成される。RAMの大容量化には、原子レベルの不均一性や凹凸によるTMR薄膜のバラツキ抑制、材料の選択が重要となるが、多結晶銅配線上へのTMR薄膜形成ではバラツキ抑制や材料の選択肢には限界があった。

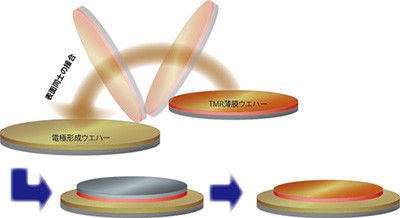

今回、同研究グループは、CMOS形成ウェハとTMR薄膜ウェハを別体形成した後に圧着して接合する、3次元積層プロセス技術によるTMR素子の作製に成功した。なお、今回の研究ではCMOS形成ウェハを銅電極形成ウェハで代用している。

同3次元積層プロセスにより、ウェハ上に銅電極層、タンタル接合層、多結晶TMR薄膜層の順に形成された3次元積層試料に微細加工を行い、サイズが28nm~65nmのMRAMデバイスを作製し、動作を確認したところ、3次元積層プロセスを行わないTMR薄膜を用いたMRAMデバイスと比較して、3次元積層プロセスを経た後のMRAMデバイスは、読出性能・書込性能はまったく劣化せず、STT-MRAMで重要な性能指標となる「データ書き込み効率」は2に達し、世界トップクラスの性能を維持していたという。

今回用いた多結晶TMR薄膜よりも単結晶TMR薄膜の方が機械的強度が強いことから、今回の3次元積層プロセスは単結晶TMR薄膜にもそのまま適用できると考えられ、同研究グループは現在、単結晶TMR薄膜の開発を進めているとしている。今後2年以内に単結晶TMR薄膜とCMOSウェハの3次元積層プロセスを確立し、5年以内に3次元積層MRAMの製品開発の着手を目指していきたい考えだ。

3次元積層プロセス技術の概要 (出所:産総研Webサイト)

※本記事は掲載時点の情報であり、最新のものとは異なる場合があります。予めご了承ください。

http://news.mynavi.jp/news/2017/05/19/278/?rt=top

産業技術総合研究所(産総研)などは5月16日、次世代の不揮発性メモリであるとされる磁気ランダムアクセスメモリ(MRAM)の3次元積層プロセス技術を開発したと発表した。

同成果は、産総研スピントロニクス研究センター金属スピントロニクスチーム 薬師寺 啓研究チーム長、集積マイクロシステム研究センター高木秀樹総括研究主幹、ウエハレベル実装研究チーム 倉島優一主任研究員、ナノエレクトロニクス研究部門3D集積システムグループ 菊地克弥研究グループ長、渡辺直也主任研究員らの研究グループによるもので、5月15日付けの国際科学誌「Applied Physics Express」に掲載された。

MRAMは、垂直磁化TMR素子をベースとする記録ビットと、ビット選択に用いる半導体トランジスタ(CMOS)、多結晶銅などの金属配線からなり、通常、垂直磁化TMR素子薄膜(TMR薄膜)は、逐次積層といってCMOS形成後に金属配線上に直接形成される。RAMの大容量化には、原子レベルの不均一性や凹凸によるTMR薄膜のバラツキ抑制、材料の選択が重要となるが、多結晶銅配線上へのTMR薄膜形成ではバラツキ抑制や材料の選択肢には限界があった。

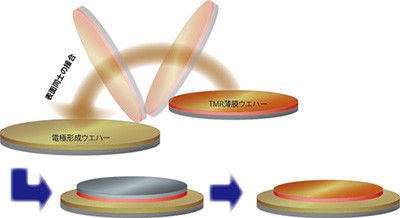

今回、同研究グループは、CMOS形成ウェハとTMR薄膜ウェハを別体形成した後に圧着して接合する、3次元積層プロセス技術によるTMR素子の作製に成功した。なお、今回の研究ではCMOS形成ウェハを銅電極形成ウェハで代用している。

同3次元積層プロセスにより、ウェハ上に銅電極層、タンタル接合層、多結晶TMR薄膜層の順に形成された3次元積層試料に微細加工を行い、サイズが28nm~65nmのMRAMデバイスを作製し、動作を確認したところ、3次元積層プロセスを行わないTMR薄膜を用いたMRAMデバイスと比較して、3次元積層プロセスを経た後のMRAMデバイスは、読出性能・書込性能はまったく劣化せず、STT-MRAMで重要な性能指標となる「データ書き込み効率」は2に達し、世界トップクラスの性能を維持していたという。

今回用いた多結晶TMR薄膜よりも単結晶TMR薄膜の方が機械的強度が強いことから、今回の3次元積層プロセスは単結晶TMR薄膜にもそのまま適用できると考えられ、同研究グループは現在、単結晶TMR薄膜の開発を進めているとしている。今後2年以内に単結晶TMR薄膜とCMOSウェハの3次元積層プロセスを確立し、5年以内に3次元積層MRAMの製品開発の着手を目指していきたい考えだ。

3次元積層プロセス技術の概要 (出所:産総研Webサイト)

※本記事は掲載時点の情報であり、最新のものとは異なる場合があります。予めご了承ください。

http://news.mynavi.jp/news/2017/05/19/278/?rt=top

引用元:http://anago.2ch.sc/test/read.cgi/bizplus/1495183940/

3: 名刺は切らしておりまして 2017/05/19(金) 17:54:25.32 ID:N1wuAC4t.net

5年以内??

もっと早くしてくれや

もっと早くしてくれや

4: 名刺は切らしておりまして 2017/05/19(金) 17:56:31.73 ID:5dXIIoBd.net

MOの新しいの?

33: 名刺は切らしておりまして 2017/05/19(金) 19:25:57.76 ID:ftXoyMWZ.net

MRAMやReRAMは情報を電荷ではなく、抵抗値を変化させることで保持します。

このため半導体回路を微細化しても、DRAMのように電荷量不足の問題は起きません。

10ナノメートル以下のプロセスの微細化にも対応できるといわれています。

MRAMやReRAMは記憶回路は比較的単純なのでDRAM並に大容量化もできるとされ、

読み書き性能もそこそこ高速なので、

今後、DRAM代替となる次世代メモリとして期待されています。

このため半導体回路を微細化しても、DRAMのように電荷量不足の問題は起きません。

10ナノメートル以下のプロセスの微細化にも対応できるといわれています。

MRAMやReRAMは記憶回路は比較的単純なのでDRAM並に大容量化もできるとされ、

読み書き性能もそこそこ高速なので、

今後、DRAM代替となる次世代メモリとして期待されています。

8: 名刺は切らしておりまして 2017/05/19(金) 18:03:25.76 ID:YR83g7Ky.net

こういうのっていつどこで実用化されて量産されてるの?

12: 名刺は切らしておりまして 2017/05/19(金) 18:16:17.41 ID:4rf1qFUU.net

>CMOS形成ウェハとTMR薄膜ウェハを

>別体形成した後に圧着して接合する

なんつー強引なwww

ちゃんとパターン合わせられるんかw

>別体形成した後に圧着して接合する

なんつー強引なwww

ちゃんとパターン合わせられるんかw

24: 名刺は切らしておりまして 2017/05/19(金) 18:57:47.24 ID:RyzxbuLF.net

>>12

あくまで実証レベルだろ。ミクロン単位オーダーで採算度外視で時間をかけて

いいなら可能かもしれんが、製品レベルでは実用にはならんだろうな。

あくまで実証レベルだろ。ミクロン単位オーダーで採算度外視で時間をかけて

いいなら可能かもしれんが、製品レベルでは実用にはならんだろうな。

28: 名刺は切らしておりまして 2017/05/19(金) 19:11:47.31 ID:6Gegx1WW.net

三次元積層プロセスっていうから、縦方向に集積させるのかと思ったら、単に記憶素子と制御素子を別々に作って後で貼り合わせるだけなのね。>>12も言ってるけど、パターンはどう合わせてるんだろう?

14: 名刺は切らしておりまして 2017/05/19(金) 18:19:44.86 ID:Ip/53mc6.net

ポストNANDフラッシュの候補のひとつだが

インテルが3D Xpointで先行してるから

本命は相変化型だろうな

インテルが3D Xpointで先行してるから

本命は相変化型だろうな

31: 名刺は切らしておりまして 2017/05/19(金) 19:24:06.22 ID:ftXoyMWZ.net

>>14

ポストDRAMの候補なんじゃないの?

不揮発性なのでデータの消えないメインメモリが用途なのでは?

DRAMの終焉――消えないメモリがもたらす大変化

http://diamond.jp/articles/-/35682?page=2

ポストDRAMの候補なんじゃないの?

不揮発性なのでデータの消えないメインメモリが用途なのでは?

DRAMの終焉――消えないメモリがもたらす大変化

http://diamond.jp/articles/-/35682?page=2

43: 名刺は切らしておりまして 2017/05/20(土) 03:33:39.72 ID:MFUegsXn.net

>>31

FLASHとDRAMの中間の位置づけだね

コンピュータのアーキテクチャを

変える可能性がある

FLASHとDRAMの中間の位置づけだね

コンピュータのアーキテクチャを

変える可能性がある

25: 名刺は切らしておりまして 2017/05/19(金) 18:58:09.17 ID:Q7JvoPP2.net

MRAMメモリ搭載の商品なんてだいぶ前からあんのに

未だに主役張れないあたり

コスパ悪いし色々問題ばっかなんだろうなって。

未だに主役張れないあたり

コスパ悪いし色々問題ばっかなんだろうなって。

29: 名刺は切らしておりまして 2017/05/19(金) 19:20:12.64 ID:RyzxbuLF.net

>>25

フラッシュメモリも、当初は旧日立(ルネサス)のワンチップマイコンZTATの

内蔵PROMとして採用されたり、従来の紫外線消去型PROMの置き換えが主流で、

当時の微細加工技術の限界もあって容量も512kバイトとかだった。

それから30年くらい経つ。MRAMは、フラッシュメモリと違ってDRAMと同様に

バイト単位で読み書きできるだけでなく、電源を切っても消えないので、

DRAMに替えてメインメモリに使えばサスペンドが不要になる。

フラッシュメモリも、当初は旧日立(ルネサス)のワンチップマイコンZTATの

内蔵PROMとして採用されたり、従来の紫外線消去型PROMの置き換えが主流で、

当時の微細加工技術の限界もあって容量も512kバイトとかだった。

それから30年くらい経つ。MRAMは、フラッシュメモリと違ってDRAMと同様に

バイト単位で読み書きできるだけでなく、電源を切っても消えないので、

DRAMに替えてメインメモリに使えばサスペンドが不要になる。

21: 名刺は切らしておりまして 2017/05/19(金) 18:42:06.89 ID:Z1gyfgPp.net

金ないのにがんばってるな

CFD販売 デスクトップPC用メモリ PC4-19200(DDR4-2400) 8GBx2枚 288pin (無期限保証)(Ballistix by Micron) W4U2400BMS-8G/WAmazon.co.jpで詳細情報を見る

posted with amastep

シー・エフ・デー販売(2016-09-10)

コメントする